CY7C1051DV33:8-Mbit(512K x 16)静态随机存取存储器

发布时间:2026/3/28

CY7C1051DV33:8-Mbit(512K x 16)静态随机存取存储器

特性

? 高速

— tAA = 10纳秒

? 消耗功率低

— 10纳秒时,ICC = 110毫安

? 低CMOS待机功耗

— ISB2 = 20 mA

? 2.0V数据保持能力

? 取消选择时自动断电

? TTL兼容输入和输出

? 具有CE和OE功能,易于内存扩展

? 提供无铅48球FBGA和44引脚TSOP II封装选项

应用

? 网络设备

? 工业控制

? 汽车电子

? 消费电子

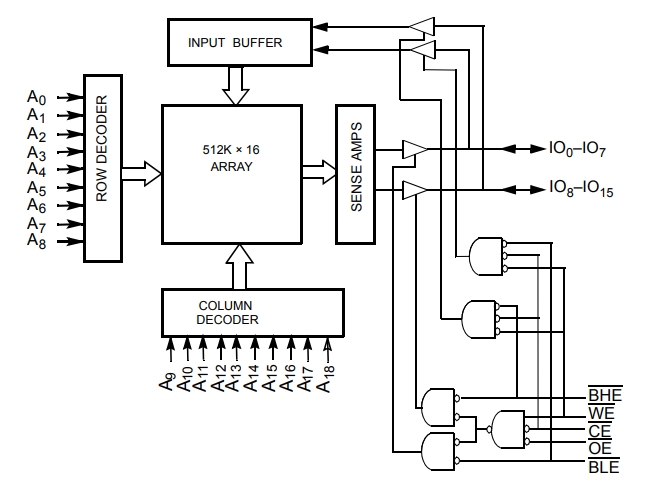

功能描述

CY7C1051DV33是一款高性能CMOS静态RAM,组织结构为512K字(每字16位)。通过将片选(CE)和写使能(WE)输入设为低电平来向该设备写入数据。如果字节低电平使能(BLE)为低电平,则将IO引脚(IO0–IO7)的数据写入地址引脚(A0–A18)指定的位置。如果字节高电平使能(BHE)为低电平,则将IO引脚(IO8–IO15)的数据写入地址引脚(A0–A18)指定的位置。

通过将芯片启用(CE)和输出启用(OE)设为低电平,同时强制将写入启用(WE)设为高电平,从设备中读取数据。如果字节低电平启用(BLE)为低电平,则地址引脚指定的内存位置的数据将出现在IO0至IO7上。如果字节高电平启用(BHE)为低电平,则内存中的数据将出现在IO8至IO15上。

当设备被取消选择(CEHIGH)、输出被禁用(OE HIGH)、BHE和BLE被禁用(BHE, BLE HIGH)或正在进行写操作(CE LOW和WE LOW)时,输入/输出引脚(IO0–IO15)将处于高阻抗状态。

CY7C1051DV33提供44引脚TSOP II封装(具有中心电源和接地引脚布局,具有创新性)以及48焊球细间距球栅阵列(FBGA)封装。

逻辑框图

工作原理

CY7C1051DV33的工作原理基于静态随机存取存储技术,通过一个十六位宽的总线接口提供数据读写功能。与传统的动态存储器不同,SRAM不需要进行周期性的刷新,存储的数据在供电状态下能够长期保持,使得操作更加简单和高效。该存储器内部由多个静态存储单元组成,每个单元由六个晶体管构成,确保了高速数据传输和低延迟的访问。

在工作过程中,CY7C1051DV33通过地址总线接收读取或写入的地址信号,其中每个地址对应一个16位的数据字。同时,通过控制信号(如片选信号和读写信号),确认数据的操作模式。内置的地址解码器能够将输入的地址信号转换为相应的存储单元,确保存储器快速定位和访问目标数据。该工作流程基于并行数据处理,使得读写速度可达35纳秒或更快,在需要高速数据处理的场景中尤为重要。

CY7C1051DV33还支持深度流水线操作,使得在进行连续的数据读写时,能够进一步提高系统性能。在执行写操作时,数据通过数据总线输入到存储单元,而在读操作时,数据则从存储单元输出至数据总线。这种机制保证了在同一时间可以进行多项操作,优化了存储器的使用效率,从而为各种复杂应用提供了充足的性能支持。

基本操作

在使用CY7C1051DV33进行基本操作时,首先需要为存储器配置一个有效的地址。设计师可以通过设置合适的地址线,选择希望进行读写的存储单元。配置完地址后,接下来将控制信号引脚设置为读或写模式,这样存储器即可根据输入信号执行相应操作。通过这种简单的设置,CY7C1051DV33能够在极短的时间内完成地址选择和数据存取。

在执行读取操作时,需将输出使能(OE)信号拉高,同时保持读写使能(WE)为低电平。此时存储器会将特定地址单元的数据输出到数据线上。该过程一旦激活,CY7C1051DV33便能够在设定的访问时间内以高速度将数据传输至微处理器或其他逻辑电路中,从而支持各种实时应用需求。

与读取操作相对应,写入操作涉及将数据存入指定的存储单元。设计者需设定控件选择写入状态,保持OE为高电平、WE为低电平,并在数据线上提供希望写入的数据。一旦该过程完成,CY7C1051DV33将立即将接收到的数据写入到指定的存储地址,确保数据的即时更新与存储的有效性。

在完成基本操作后,用户可以通过监测状态引脚的变更来验证数据的读写是否成功。这一反馈机制可以帮助设计师及时发现潜在的问题,并对系统的性能进行调整与优化。通过合理配置和使用CY7C1051DV33,设计者能够在多种应用中实现高效的数据处理和存储管理。

扫一扫,关注我们

扫一扫,关注我们